既然CPU不会从主存里读数据,那MDR有什么用呢?

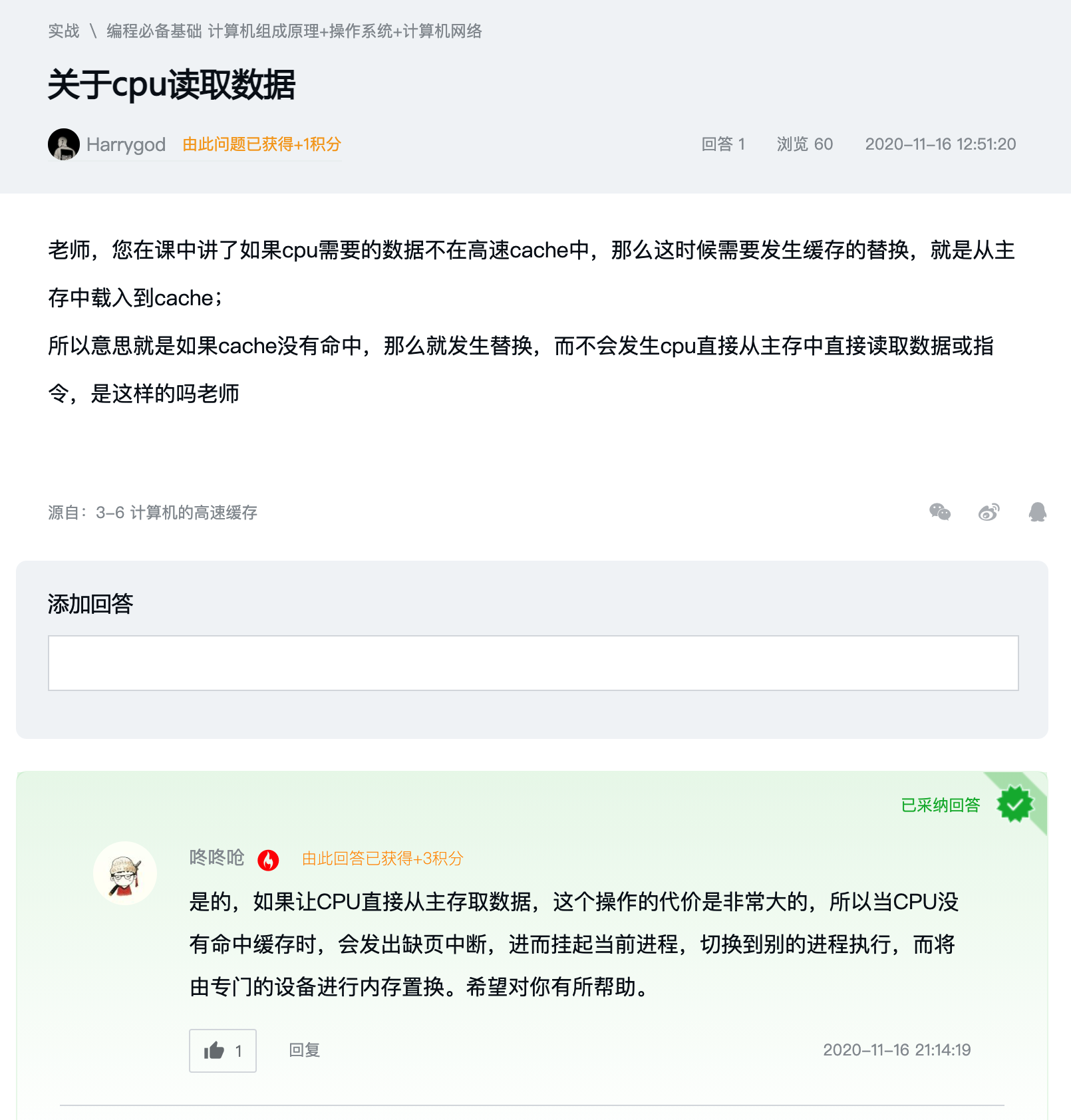

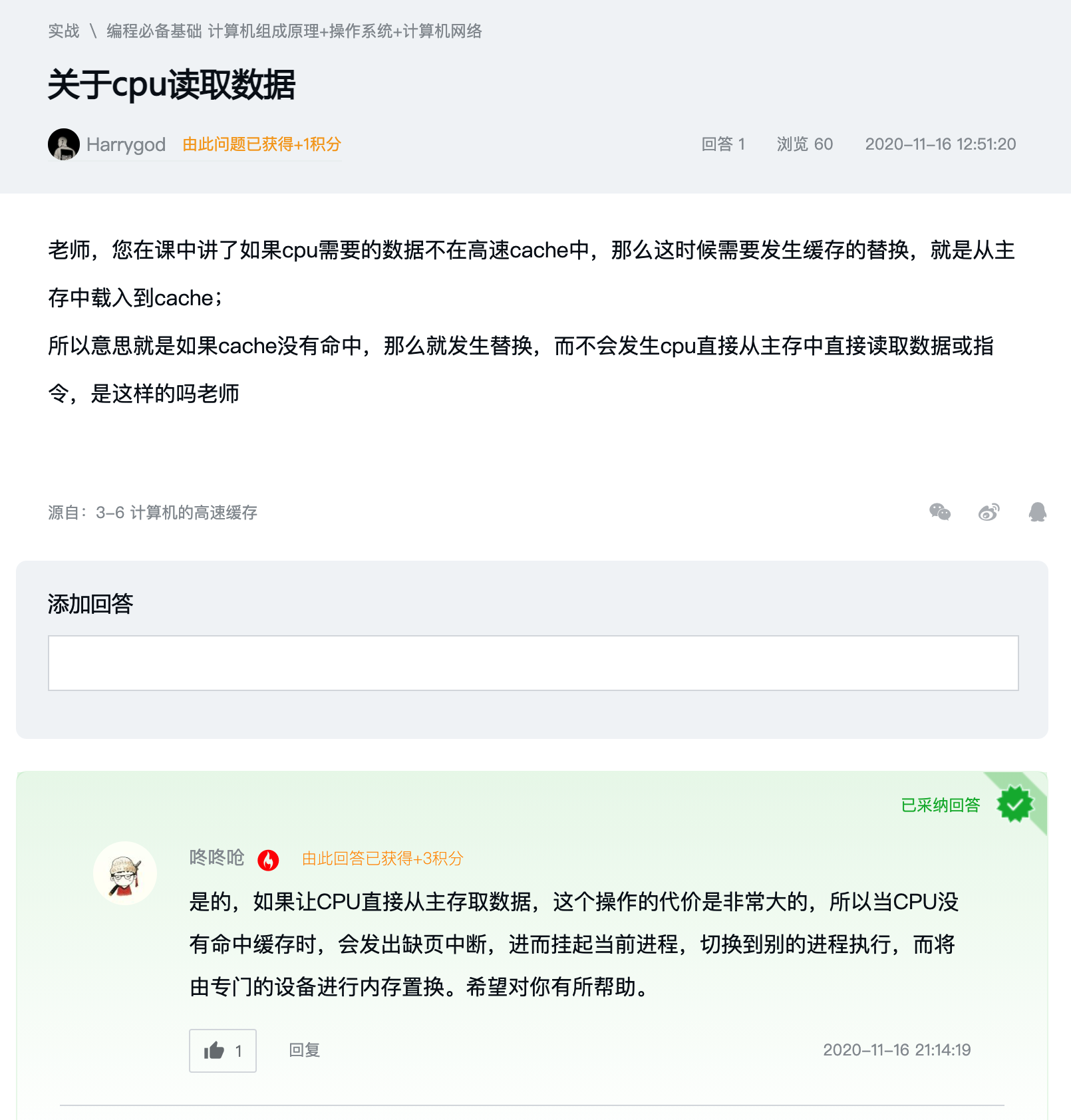

我在看老师您回答同学们的提问的时候,发现老师一直重复强调同一个观点:

CPU不会从主存中读取数据;假如CPU需要的数据不在高速缓存里,CPU会等CPU高速缓存从主存里取数据;然后CPU再从高速缓存里取数据

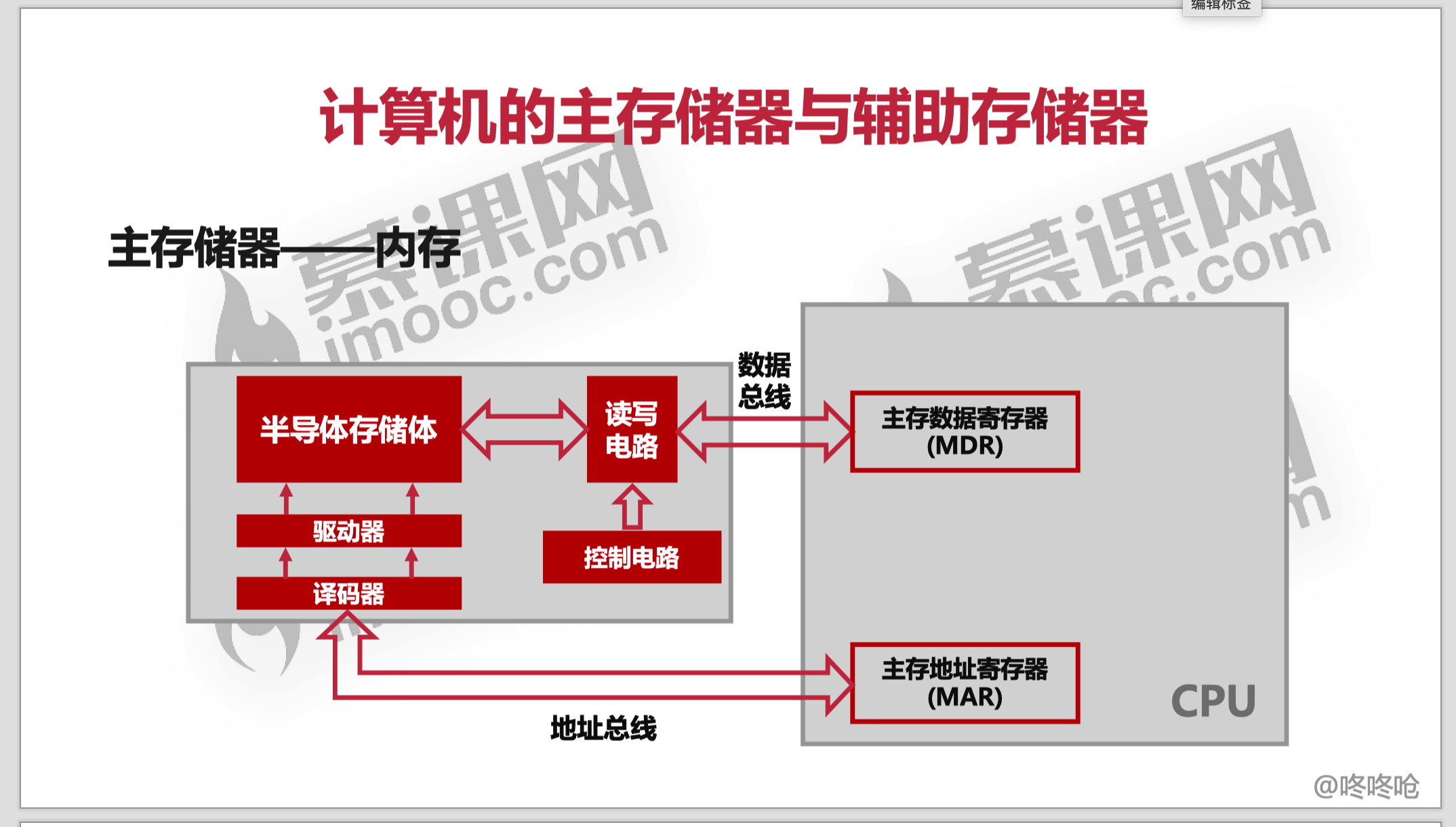

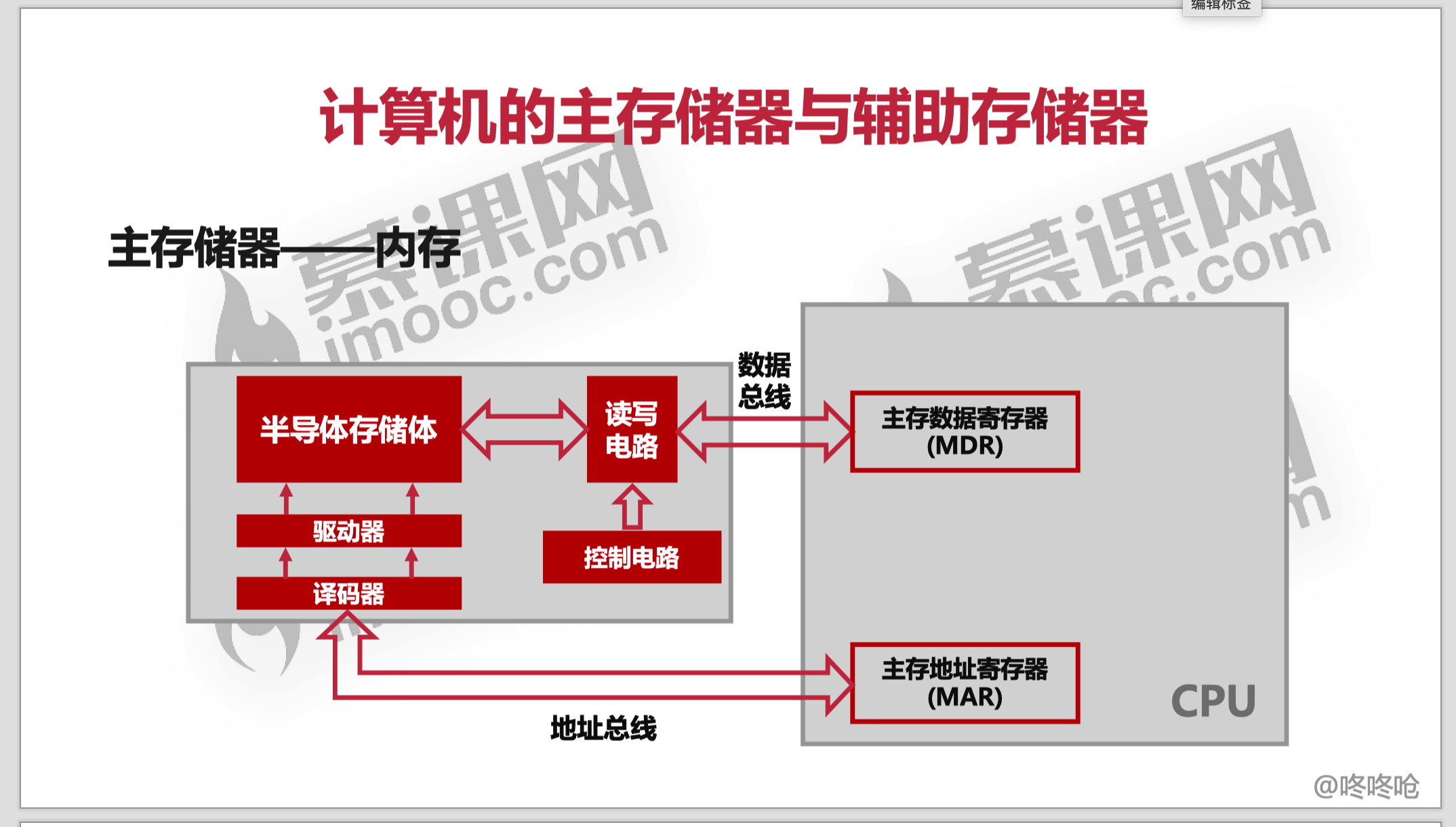

假设CPU真的不会从主存里面取数据,那么MDR这个主存数据读取器,有什么用?

6488

收起

我在看老师您回答同学们的提问的时候,发现老师一直重复强调同一个观点:

CPU不会从主存中读取数据;假如CPU需要的数据不在高速缓存里,CPU会等CPU高速缓存从主存里取数据;然后CPU再从高速缓存里取数据

假设CPU真的不会从主存里面取数据,那么MDR这个主存数据读取器,有什么用?